|

Release 3GPP Compliant Turbo decoder IP Core (May, 2000)

Release 3GPP Compliant Turbo decoder IP Core (May, 2000)

softDSP released 3GPP compliant Turbo decoder

IP core in May, 2000. We also supply simulation program and C-source code,

designer's guide, test vector, interleaver generation C source code. Powerful

decoding performance and small-size implementation will meet your system

requirements satisfactorily. softDSP Turbo decoder has the feature of easy I/O

interface and used as a slave device controlled by host processor such as ARM

core or any other DSP processor. It is recommended that every other part of 3GPP

FDD blocks except Turbo decoder is implemented by s/w (dsp) for the such

conditions as control oriented feature, easy updating, and development time

reduction.

You may be working on system

performance modeling, system implementation or you may require help with the

implementation of a specific component. We work at all stages of the system

design of channel coding and our expertise together with our hardware or

software implementations will allow you to rapidly achieve your objectives.

Simulation, Modeling

and Hardware design of Forward Error Correcting Code

Our flexible, powerful, bit-accurate

C/C++ models of Viterbi decoder and Turbo decoder enable you to simulate

complete forward error-correction systems. The detailed and precise results will

help you to predict and optimize the performance of your system. Our hardware

design modules and systems are available as reusable Intellectual Property (IP)

components or customized designs, in VHDL. Recently, Turbo decoder satisfying

3GPP standard was developed. The design has been optimized for power and gate

count minimization. It can be applied to various systems as 3GPP, satellite

communication system, magnetic storage channel

softDSP released 3GPP compliant Turbo decoder

IP core in May, 2000. We also supply simulation program and C-source code,

designer's guide, test vector, interleaver generation C source code. Powerful

decoding performance and small-size implementation will meet your system

requirements satisfactorily. softDSP Turbo decoder has the feature of easy I/O

interface and used as a slave device controlled by host processor such as ARM

core or any other DSP processor. It is recommended that every other part of 3GPP

FDD blocks except Turbo decoder is implemented by s/w (dsp) for the such

conditions as control oriented feature, easy updating, and development time

reduction.

You may be working on system

performance modeling, system implementation or you may require help with the

implementation of a specific component. We work at all stages of the system

design of channel coding and our expertise together with our hardware or

software implementations will allow you to rapidly achieve your objectives.

Simulation, Modeling

and Hardware design of FEC.

Our flexible, powerful, bit-accurate

C/C++ models of Viterbi decoder and Turbo decoder enable you to simulate

complete forward error-correction systems. The detailed and precise results will

help you to predict and optimize the performance of your system. Our hardware

design modules and systems are available as reusable Intellectual Property (IP)

components or customized designs, in VHDL. Recently, Turbo decoder satisfying

3GPP standard was developed. The design has been optimized for power and gate

count minimization. It can be applied to various systems as 3GPP, satellite

communication system, magnetic storage channel

softDSP Turbo decoder core

softDSP

Corp. developed Turbo decoder core version 1.2 in May 2000. Powerful new technology

was adopted and it satisfies recent 3GPP standard specification (3GPP 3G TS

25.212 V.3.2.0). The detailed features are as follows.

- Use max-log-MAP decoder as an

internal component decoder which produces better performance than the other

component decoder

- Use sliding-window technology

to reduce internal memory size

- Constraint length K=4 (8-state

with g0=1+D2+D3, g1=1+D+D3), rate 1/2, 1/3

- 4-8 bit soft input (recommend

over 5bit input) with internal 8bit fixed-point processing

- Support 8-level Eb/N0 scaling

- 3GPP compliant (block size 40-5114)

- Easy to use interface, easy to

modify or adapt

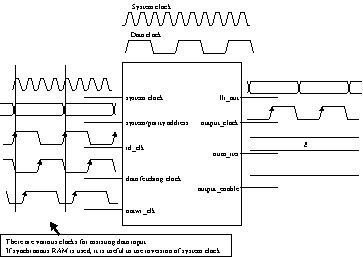

Figure. Design timing

diagram of Turbo decoder

3GPP

Channel coding (FDD point of view)

When designing 3GPP baseband modem

systems, such blocks as error detection, block segmentation, rate matching,

and interleaving can be implemented by DSP processor, since DSP has the advantage

in complex control oriented operations, I/O intensive operations, and memory

referencing, and further for the future extension or flexibility, these blocks can be implemented by DSP coding.

But for the case of error correcting

codes, since the encoder standard is fixed and decoder is very computation oriented,

it is advantageous to implement it hardwired. The considering point will be

such point as small gate size, performance, speed, and easy I/O interface. So

easy and independent decoder design is important. To focus these point we developed

and modified our design. By employing max-log-MAP method, reduced computation

complexity without sacrificing the performance. Further, for the features of

rate matching algorithm in 3GPP FDD standard, the information of the front

channel estimator can be inexact, which gives more plausible reasons to select

max-log-MAP method as the best candidate for component decoder of Turbo code.

Also, by employing sliding-window

technology, required memory size was reduced significantly. Comparing with normal MAP decoder

implementation, just about 10% of memory is required. Also, by various and

exhaustive simulation

and design of each blocks, we could make optimally designed code. softDSP turbo decoder core was fully

designed by VHDL code which gives flexibility to ASIC and system design.

Offering

materials

- VHDL source code

- Test C-source code (floating point

and fixed point)

- Interleaver generation routine

C-source (3G TS 25.212 V.3.2.0)

- Test data vector

|